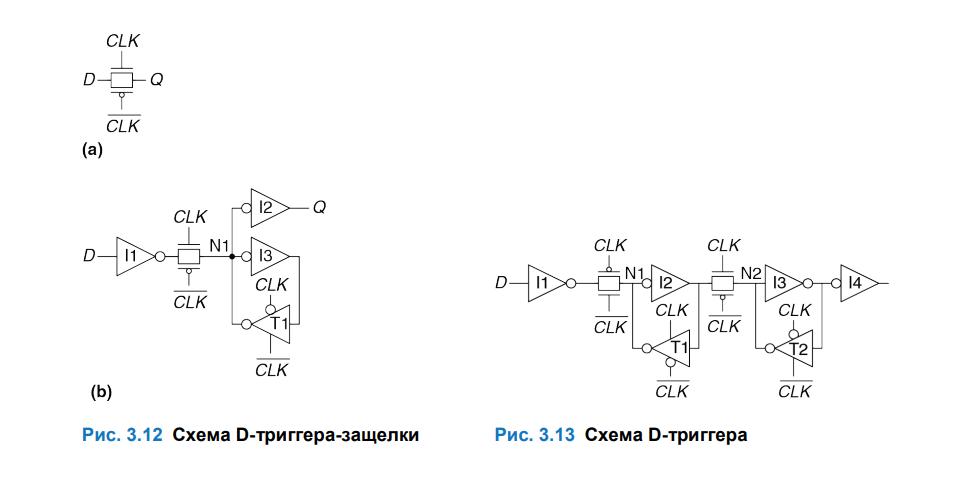

Читаю книгу Цифровая схемотехника и архитектура компьютера и дошел до момента описания D триггера, а именно проектирование на транзисторном уровне.

Автор говорит что простую D защелку можно сделать из одного проходного вентиля, но как это возможно если проходной вентиль просто пропускает или не пропускает бит информации, но никак не сохраняет его, т.е у него нет состояния, а защелка по определению должна его иметь.

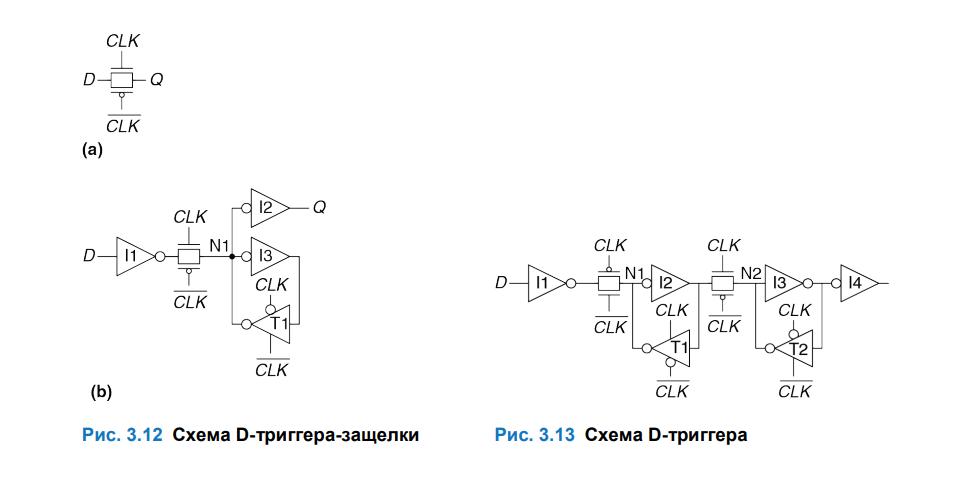

И дальше автор описывает "усовершенстованную" защелку и триггер с использованием буфферов.

Подскажите какую роль они играю в построении, зачем они вообще нужны и как работают. И описания в книге вообще не понял что к чему и как. Для чего нужны L1, L2, L3, а также T1 с тремя состояниями. Как вообще устроен механизм сохранения состояния в данных схемах?