я не имел ввиду допустимые уровни шумов между выходом одного вентеля и входом другого, я имел ввиду вход и выход одного вентеля, описанные передаточной характеристикой.

Видимо, вы не понимаете, что и для множества разных логических элементов, и для единственного

это одно и то же. Дело тут в строгой стандартизации вида ПХ для всех элементов одной логической серии. Когда-то в старинных справочниках рисовали вид ПХ отдельно для инверторов, отдельно для И-НЕ, отдельно для ИЛИ-НЕ и т.д., но потом, когда дошло, что разница в их начертании настолько незначительна, что её можно игнорировать, это делать перестали.

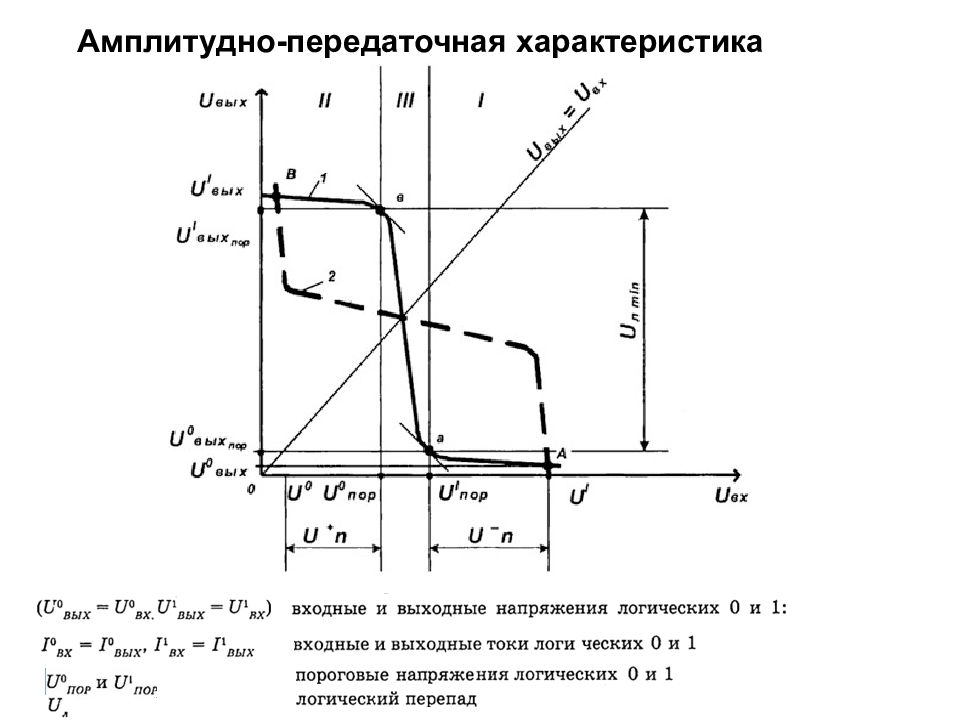

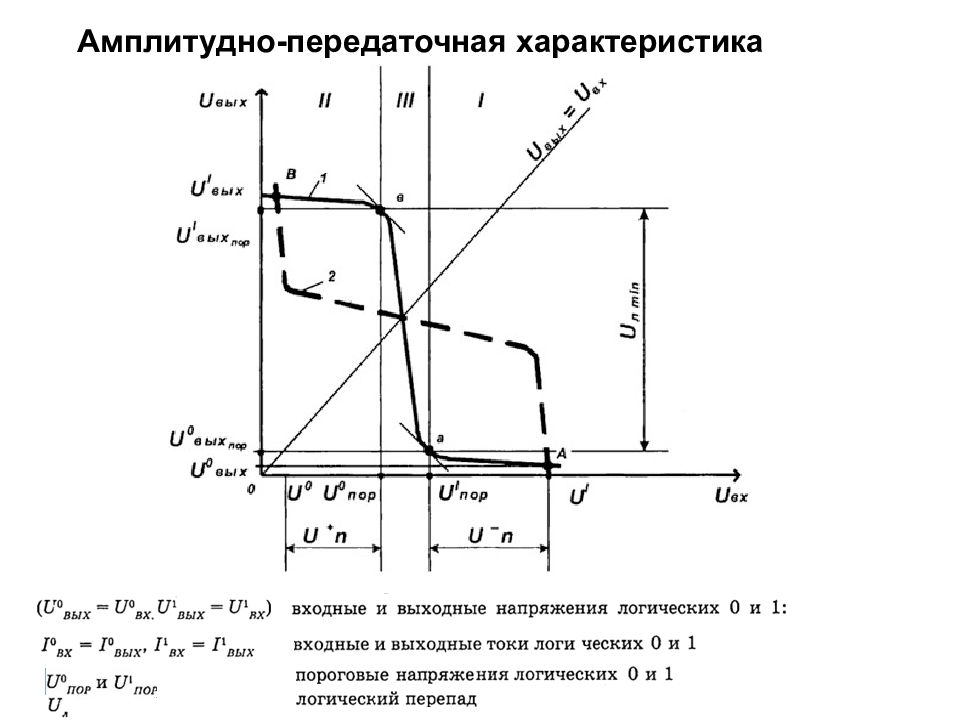

Единственный случай, когда приходится рассматривать ПХ одного логического элемента - это при графическом расчёте пороговой точки ПХ методом наложения её самой на себя с разворотом на 90 градусов (ведь выходной сигнал одного элемента - это входной для другого). Получившееся перекрестие сразу показывает условное пороговое напряжение, пролетая которое, сигнал меняет своё значение с 0 на 1 или наоборот. Вот иллюстрация:

Для CMOS-серий это пороговое напряжение примерно равно половине напряжения питания, а для TTL - примерно 1,4...1,5 вольт.

вроде понял: если изменение напряжения на выходе происходит быстрее, чем на входе. то такой промежуток следует расположить в запретной зоне, т.к любая помеха будет многократно усилена.

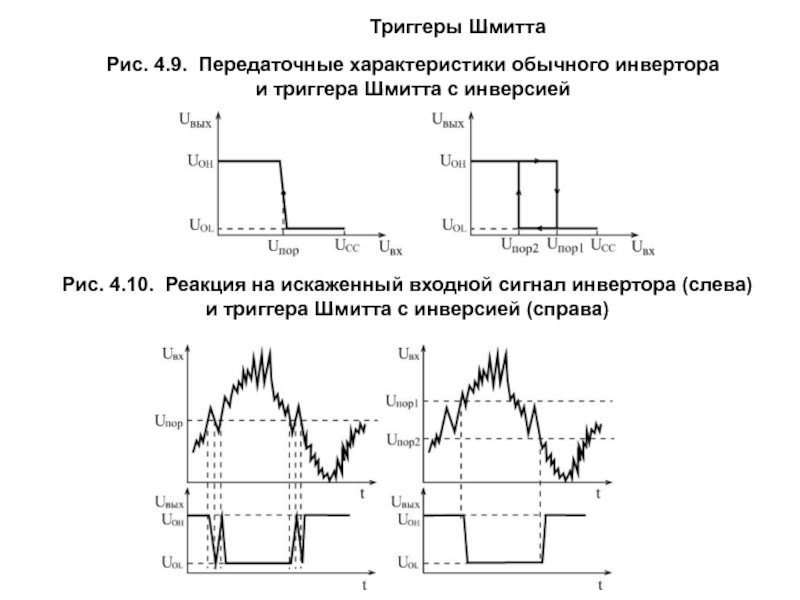

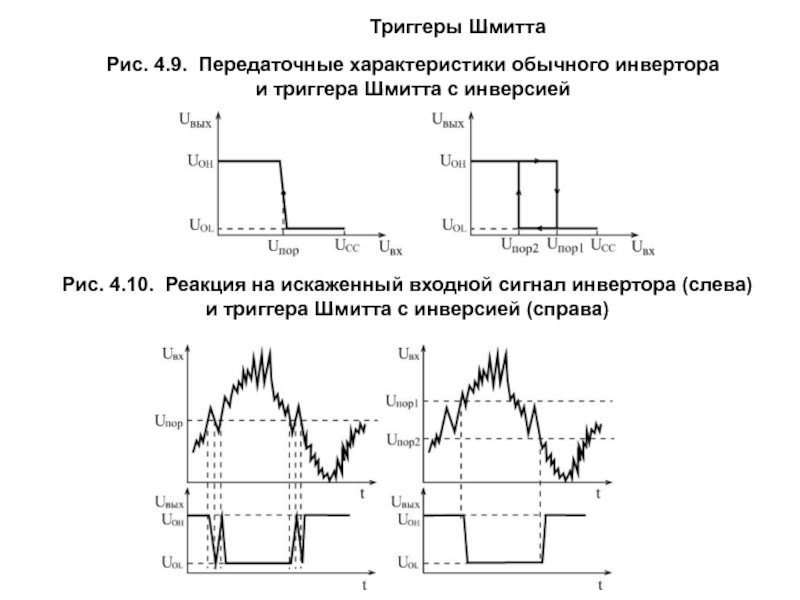

Всё, что вам доступно при проектировании логического элемента - это манипуляция напряжениями перегиба ПХ для верхнего и нижнего ключей, чтобы результирующая ПХ была примерно симметрична. Впрочем, для повышения стойкости логики к помехам есть и другие методы - например, введение разных порогов срабатывания для перехода от 0 к 1 и от 1 к 0 (это т.н. "триггер Шмитта".) Вот как это выглядит:

Слева -- ПХ обычного логического элемента, и соответственно, вид сигнала с прошедшей на выход помехой, справа - то же самое для элемента с триггерной ПХ, у него помеха на выход не проходит.

Надеюсь, ничего не упустил из интересующего вас. Если упустил - пишите в комментарии, будем прояснять.

Слева -- ПХ обычного логического элемента, и соответственно, вид сигнала с прошедшей на выход помехой, справа - то же самое для элемента с триггерной ПХ, у него помеха на выход не проходит.

Слева -- ПХ обычного логического элемента, и соответственно, вид сигнала с прошедшей на выход помехой, справа - то же самое для элемента с триггерной ПХ, у него помеха на выход не проходит.