-- code testing 'logic'

library ieee;

use ieee.std_logic_1164.all;

--Description interface the system. As this is a test file,

--the system interface is always empty

entity logic_tb is

end logic_tb;

--Description behavior

architecture logic_behavior_test of logic_tb is

--Description of test component

component logic

port (

I1: in std_ulogic; --first_input

I2: in std_ulogic; --second_input

I3: in std_ulogic; --second_input

I4: in std_ulogic; --second_input

I5: in std_ulogic; --second_input

Q1: out std_ulogic; --direct outputs

Q2: out std_ulogic; --inverse outputs

Q3: out std_ulogic; --inverse outputs

Q4: out std_ulogic; --inverse outputs

TT2: out std_ulogic --inverse outputs

);

end component;

--reservation of all used signals

signal I1, I2, I3, I4, I5, Q1, Q2, Q3, Q4, TT2: std_ulogic;

begin

--mapping signal with interface system

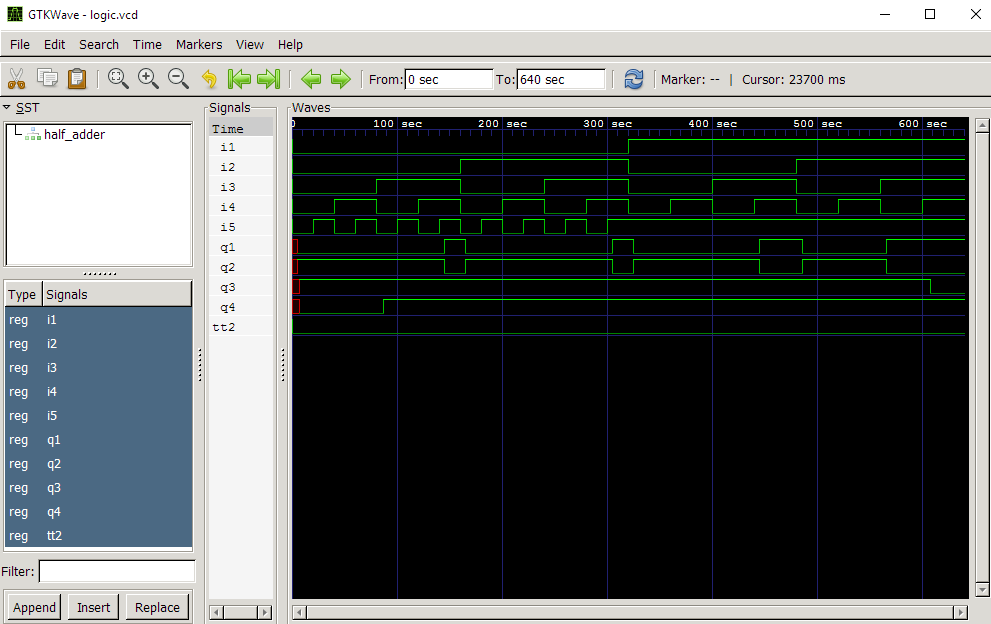

half_adder: logic port map(I1 => I1, I2 => I2, I3 => I3, I4 => I4, I5 => I5, Q1 => Q1, Q2 => Q2, Q3 => Q3, Q4 => Q4, TT2 => TT2);

--process testing

process begin

I1 <= '0';

I2 <= '0';

I3 <= '0';

I4 <= '0';

I5 <= '0';

TT2 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '0';

I3 <= '0';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '0';

I2 <= '0';

I3 <= '0';

I4 <= '1';

I5 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '0';

I3 <= '0';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '0';

I2 <= '0';

I3 <= '1';

I4 <= '0';

I5 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '0';

I3 <= '1';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '0';

I2 <= '0';

I3 <= '1';

I4 <= '1';

I5 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '0';

I3 <= '1';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '0';

I4 <= '0';

I5 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '0';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '0';

I4 <= '1';

I5 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '0';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '1';

I4 <= '0';

I5 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '1';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '1';

I4 <= '1';

I5 <= '0';

wait for 20000 ms;

I1 <= '0';

I2 <= '1';

I3 <= '1';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '0';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '0';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '0';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '0';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '1';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '1';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '1';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '0';

I3 <= '1';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '0';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '0';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '0';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '0';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '1';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '1';

I4 <= '0';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '1';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

I1 <= '1';

I2 <= '1';

I3 <= '1';

I4 <= '1';

I5 <= '1';

wait for 20000 ms;

wait;

end process;

end logic_behavior_test;