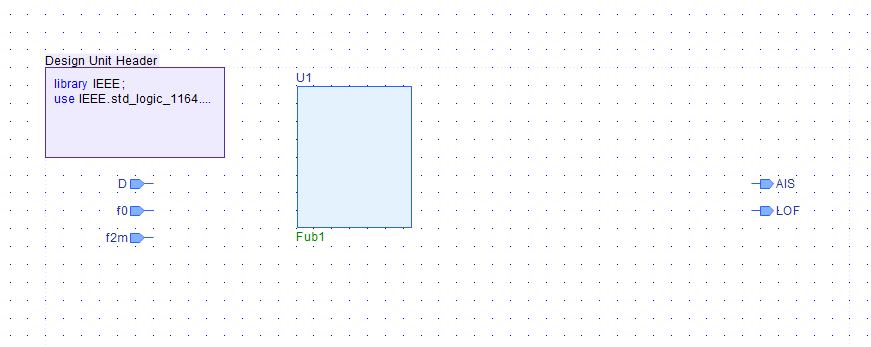

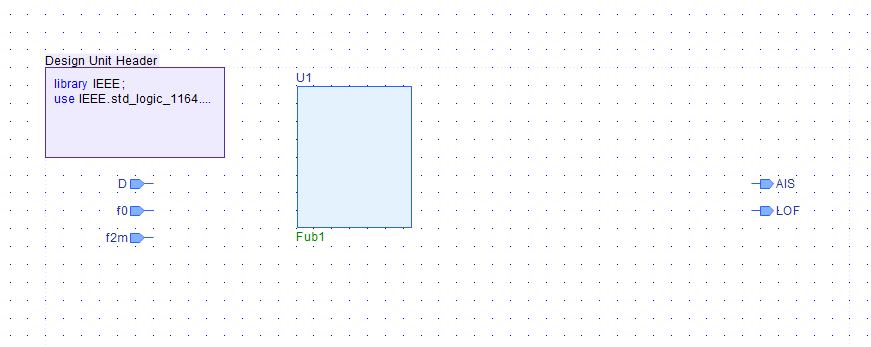

Добрый день хочу к вам обратиться с вопросом, как смоделировать индикатор аварии цикла на языке VHDL в программе ActiveHDL. На вход поступают: D- данные 1\0, f0 метка цикла и цикловая синхронизация. На выходе сигналы AIS и LOF.

Насколько я понял, когда приходят f0- метка цикла и f2m- цикловая синхронизация, то все хорошо, если что то из них не приходит то на выход AIS отсылаем единицы.

Если на входе D: 1-то все норм, если 0 то что отправляем на вход LOF?

И как написать программу для управления всем этим?